P.S. Software House Marketing And Research Co. P.O. Box 966 Mishawaka, IN 46544

(219) 255-3408

#### Dear PET owner;

Thank you for your order. We at PET-SHACK take great Pride in our Products and hope you are completely satisfied. In fact we Guarantee your satisfaction or we will Sadly but Promptly refund your money.

Take a look at the enclosed list of our Fine Products and see if there is anything else we can serve you with.

We solicit your suggestions on improvements and New products.

We hope to be able to serve you again.

Sincerely.

Larry R. Shallenberger Pr

President

P.S. Software House Marketing And Research Co. P.O. Box 966 Mishawaka, IN 46544

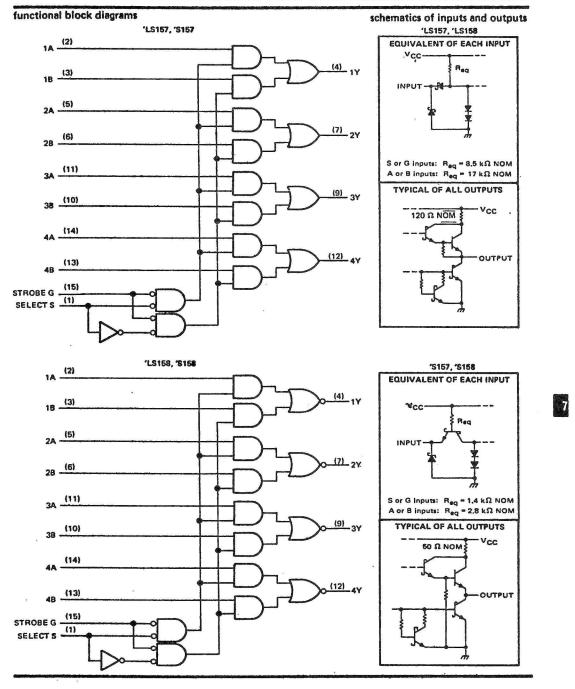

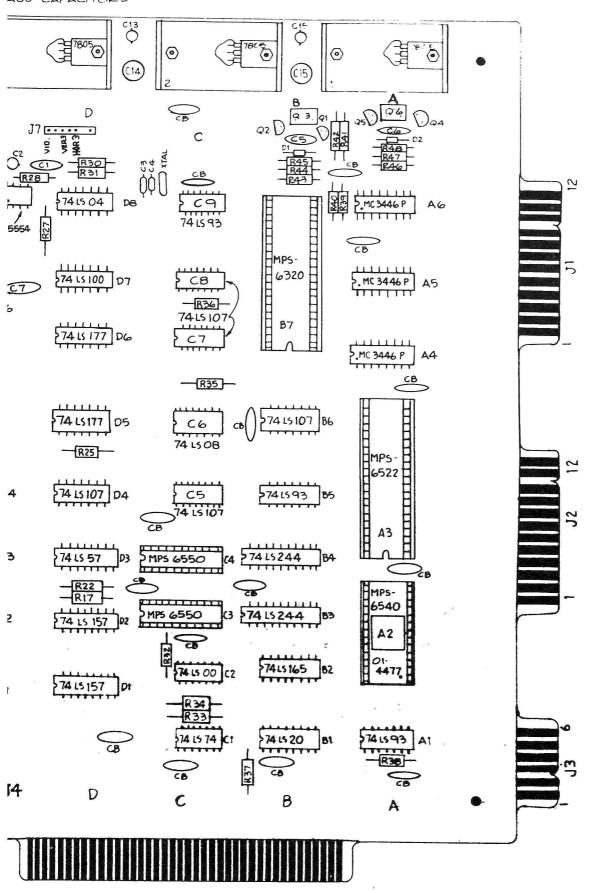

ERRATA: Corrections and Differences for the PET schematics.

On the CPU board layout, three misprints were found.

G1 should be SN74154 E4 should be 74LS154 B7 should be 6520

It was brought to my attention by one of my customers that on his PET the ROM's are 24 pin #901447-01 to 07 with the 01's being replaced by 09's to eliminate the problem of losing the curser. With this series, there is no need for additional chips for decoding or inverting signals. I do not have the pin-outs for this series as of yet. After I have compiled a substantial list of changes, I will send this list to all who requist it.

#### **PETSHACK Software House**

MARKETING AND RESEARCH COMPANY

P. O. Box 966 Mishawaka, Indiana 46544

(219) 255 3408

Re. ROM & RAM chips:

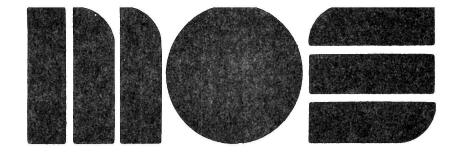

The ROM chips and the RAM chips used in your PET may not be the same as used in the authors PET. According to the best information I have been able to get at this time, Commodore is using two different chips of each. For the RAM's they are using either the 6550 or the 2114(6114) and for the ROM's they are either using the 6540 or the 2316(6316). Even though the pin-outs are different, the function is identical so the actual wireing should be identical, with the exception of the Chip Select lines.

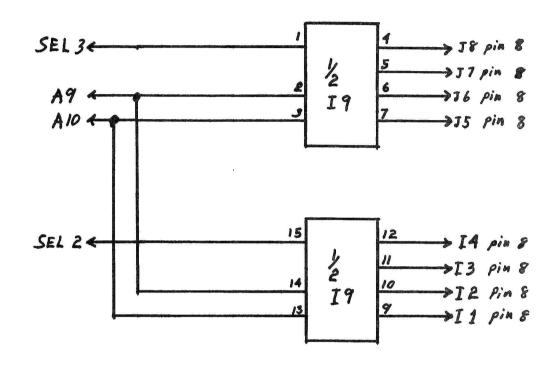

Where the 2316 is used in place of the 6540, inverters have to be added in line to two of the Chip Select lines (CS1,CS2, or CS3). The implementation of the 2114 in place of the 6550 is a bit more difficult in that it has only one Chip Select line. A 74LS139 has to be added to decode the Address lines to replace the missing Chip Select lines. A partial schematic is included to show the changes.

Enclosed in this package are the specification and Pin-Out sheets of all five chips mentioned.

If you find any other differences, I would appreciate it if you would let me know so that I can update future schematics.

LARRY R. SHALLENBERGER

President

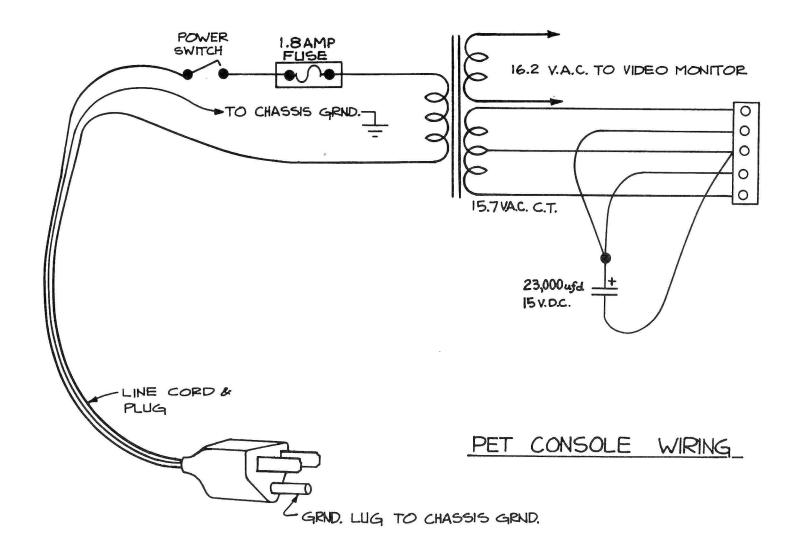

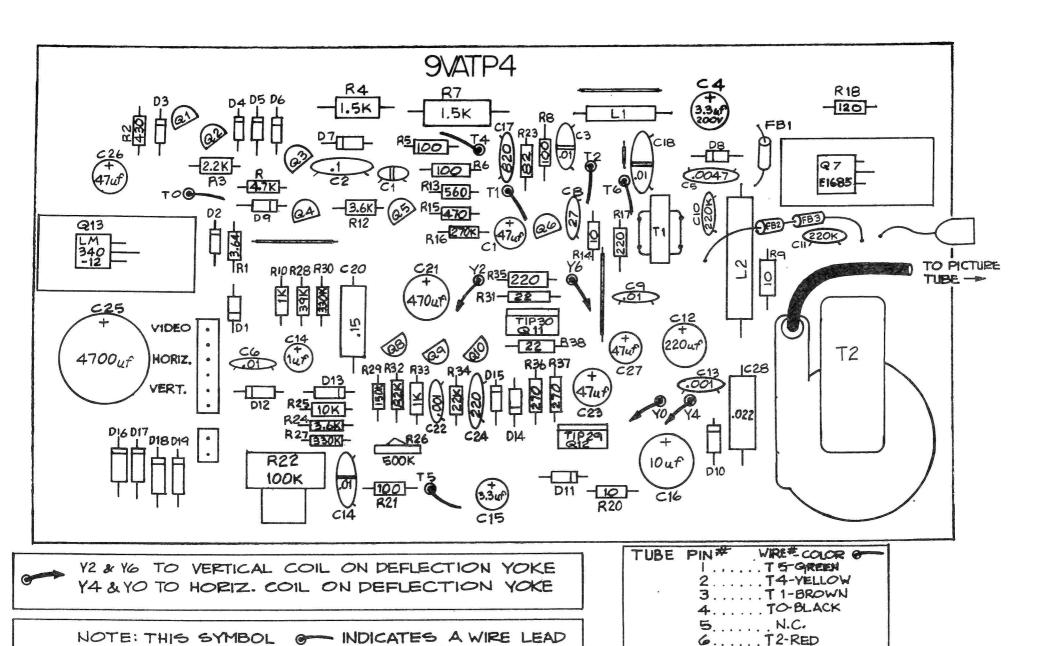

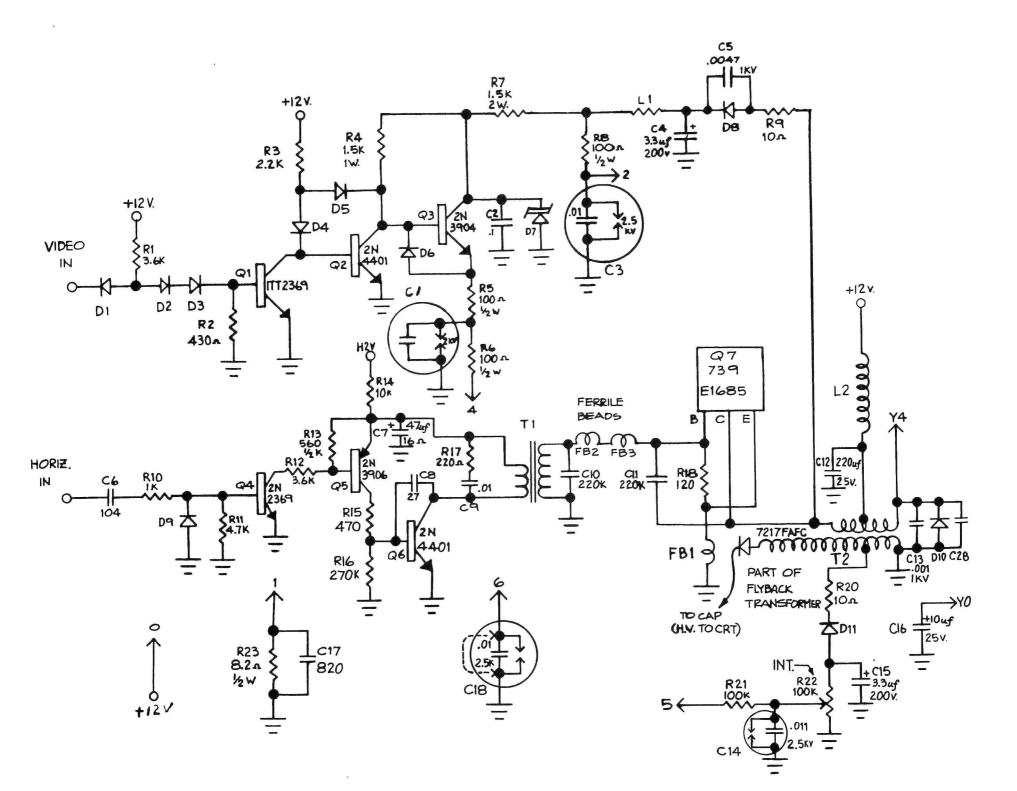

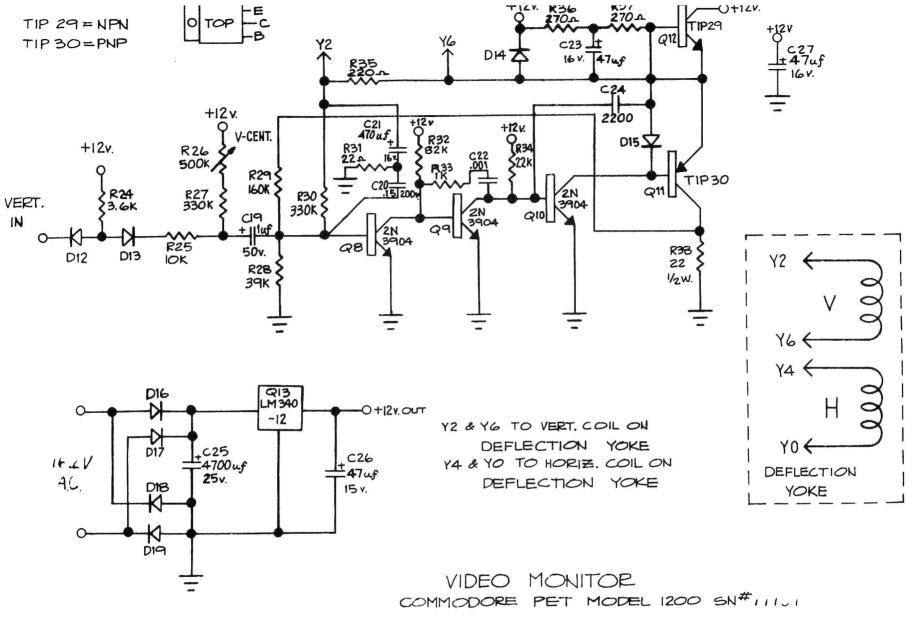

VIDEO MONITOR

. TG-BLUE

ENDING @ DEFLECTION YOKE (MARKED"Y") OR

CRT (TUBE; MARKED"T").

PET KEYBOARD

|                                   | 7<br>H     | 4 I        | E e            | ω <sup>I</sup> | ōı         |

|-----------------------------------|------------|------------|----------------|----------------|------------|

|                                   | - I        | w I        | υ I            | 7<br>H         | ع =        |

| ø ·                               | 2 5        | 4 2        | 95             | 00 U           | ō a        |

| O ·                               | _ v        | m 9        | 20             | 7              | 0 J        |

| ቢ .<br>ጡ .<br>ጠ .                 |            |            |                |                |            |

| ₩.<br><br>I.                      | - L        | ш<br>Г     | ro<br>Tr       | 7 4            | L<br>T     |

| 4 ·                               | 2<br>E     | 4 ш        | 9 ш            | øу<br>пл       | <u>б</u> щ |

| o.                                | _ ш        | <u>м</u> ш | <u>м</u>       | ر<br>آ         | 2 ш        |

| Ø.                                | 2<br>D     | 4 0        | ٥              | ∞ <sub>□</sub> | ō0         |

| <u>ō</u> ∙<br>ℓ.                  | ے ۵        | w 0        | ν <sub>0</sub> | 7 0            | 00         |

| ו א'כ'                            | 20         | 4 0        | Ue             | ω U            | Ōυ         |

| J.N —   I ·                       | - U        | m U        | ں م            | ر<br>ر         | σV         |

|                                   | 2<br>B     | 4 @        | ه و            | ω<br>Ω         | <u>o</u> a |

| · ·                               | <u>-</u> a | <i>m</i>   | w w            | 7<br>B         | 2 0        |

| NOT USED:<br>2F<br>4F<br>6F<br>0F | 7<br>A     | 4 4        | <b>6</b>       | ω <            | <u>0</u> ∢ |

| Λ<br>Γ α 4 9 Ø Ō                  | - d        | <i>w</i> ∢ | ω ∢            | ۲<br>4         | σ ∢        |

|                                   |            |            |                |                |            |

EACH NUMBER AND LETTER COMBINATION IN THE SQUARES ABOVE (KEY BOARD KEYS) REFERS TO THE CORRESPONDING NUMBER AND LETTER ON THE CONNECTOR J-5 (SEE PARTS LAYOUT). NOTE:

Temp Drawing

# 6550 RANDOM ACCESS MEMORY

$(1024 \times 4)$

The 6550 is a high performance, low power, 4K bit, static, read/write random access memory organized as 1024 words by 4 bits per word. It operates on a single 5V power supply and requires minimum buffering and CS decoding.

All interface signal levels are identical to TTL specification, providing high noise immunity and simplified system design. All inputs are purely capacitive MOS loads with no DC current requirements. The output will drive two standard TTL loads and 100 pf.

The 6550 cycle operation is controlled by the  $\emptyset_2$  Clock. Addresses are presented to the address pin when  $\emptyset_2$  Clock is low and are latched on chip to the rising edge of the  $\emptyset_2$  Clock. The Chip Select and Read/Write signals are static and can be presented to the memory at any time. Data In and Data Out signals share common I/O pins and are unable to receive or transmit data when  $\emptyset_2$  Clock is high.

The 6550 outputs are in the high impedance state whenever the memory is de-selected,  $\emptyset_2$  Clock is low or Read/Write is low.

#### **FEATURES**

1K × 4 Organization Single 5V Power Supply Full TTL Compatibility Four CS Inputs Fully Static Data Storage - No Refreshing

High Speed - Access Times Down to 200 ns

Low Operating Power - 450 mW Typical

Single Phase TTL Level Clock

High Output Drive - Two Standard TTL Load and 100 pf

#### PIN CONNECTIONS

|     |                | enconstant and |                | -   |                            |

|-----|----------------|----------------|----------------|-----|----------------------------|

| Pin | Function       | Pin            | Function       | Pin | <u>Function</u>            |

| 1   | $A_0$          | 8              | A <sub>6</sub> | 15  | DB <sub>2</sub>            |

| 2   | $A_1$          | 9              | A7             | 16  | DB <sub>3</sub>            |

| 3   | A <sub>2</sub> | 10             | Ag             | 17  | $\mathbf{v}_{\mathtt{DD}}$ |

| 4   | A <sub>3</sub> | 11             | Ag             | 18  | CS <sub>4</sub>            |

| 5   | Au             | 12             | R/W            | 19  | CS <sub>3</sub>            |

| 6   | A <sub>5</sub> | 13             | $DB_0$         | 20  | CS <sub>2</sub>            |

| 7   | Ø <sub>2</sub> | 14             | $DB_1$         | 21  | $cs_1$                     |

|     |                |                |                | 22  | v <sub>ss</sub>            |

PRELIMINARY DATA SHEET

JULY 1977

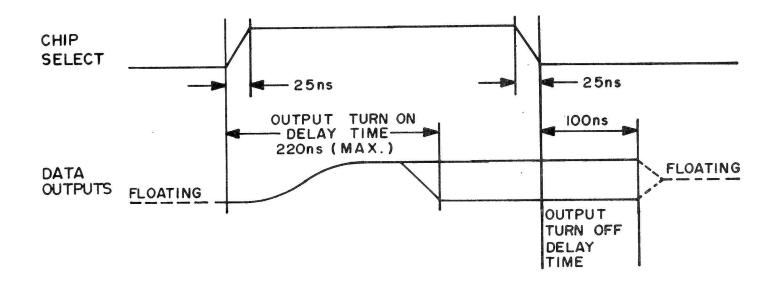

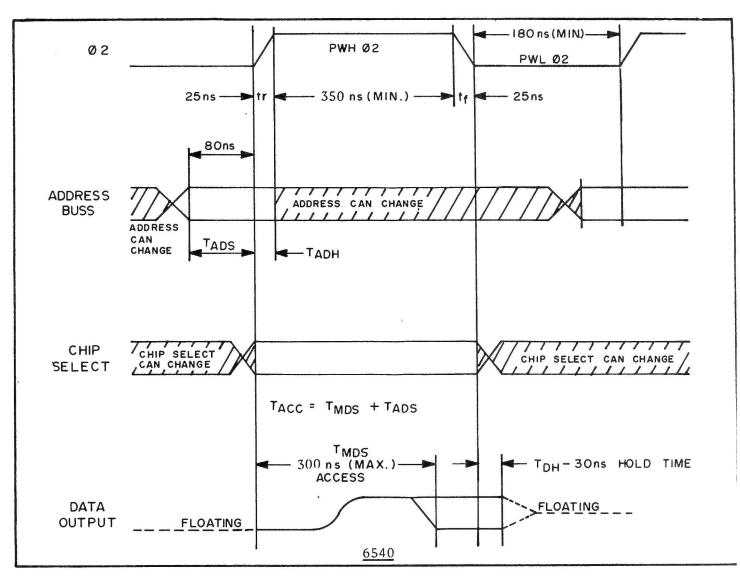

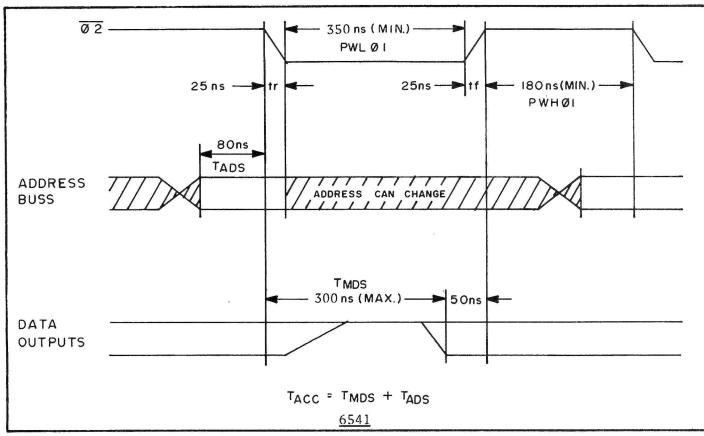

### 6540/6541

READ ONLY MEMORIES

The 6540 and 6541 16K Read Only Memories are monolithic N-channel metalgate arrays manufactured with a low-threshold process and utilizing both enhancement and depletion mode MOS transistors.

Three-state outputs provide bus-compatibility with microprocessor-based memory systems. The ROM's are organized as 2048 words of 8 bits each.

Mask options provide user specification of chip select equations, allowing addressing anywhere within a 65K memory space without external decode circuitry (6540).

#### **FEATURES**

Interface with TTL, DTL or MOS

Single +5V supply

High speed operation

(300 ns access)

Three-state outputs

Complete address control

No external components required

No system slow-down

Five chip selects (6540)

Two chip selects (6541)

#### MAXIMUM RATINGS

| RATING                | SYMBOL           | VOLTAGE      | UNIT |

|-----------------------|------------------|--------------|------|

| Supply Voltage        | v <sub>cc</sub>  | -0.3 to +7.0 | v    |

| Input/Output Voltage  | V <sub>IN</sub>  | -0.3 to +7.0 | v    |

| Operating Temperature | TOP              | 0 to 70      | °C   |

| Storage Temperature   | <sup>T</sup> STG | -55 to +150  | °C   |

## ELECTRICAL CHARACTERISTICS $(V_{CC} = 5.0 \text{ V} \pm 5\% \text{ V}_{SS} = 0 \text{ V}; T_A = 25^{\circ}\text{C})$

| CHARACTERISTIC                                                                                                | SYMBOL               | MIN.    | TYP. | MAX.            | UNIT |

|---------------------------------------------------------------------------------------------------------------|----------------------|---------|------|-----------------|------|

| Input High Voltage                                                                                            | $v_{_{\mathrm{IH}}}$ | Vss+2.0 | -    | v <sub>cc</sub> | v    |

| Input Low Voltage                                                                                             | v <sub>IN</sub>      | Vss3    | -    | Vss+.8          | v    |

| Input Leakage Current (A <sub>0</sub> -A <sub>10</sub> , C <sub>S1</sub> , C <sub>S2</sub> , Ø <sub>2</sub> ) | IIN                  |         | 1.0  | 2.5             | μA   |

| Leakage Current for High<br>Impedance (Three State)<br>Outputs: V <sub>IN</sub> = 0.4 V<br>to 2.4 V           |                      |         | 1.0  | 10.0            | μА   |

| Output High Voltage:  V <sub>CC</sub> = Min                                                                   |                      |         |      |                 |      |

| I <sub>LOAD</sub> ≤ -100μA                                                                                    | v <sub>OH</sub>      | Vss+2.4 |      |                 | v    |

| Output Low Voltage  V <sub>CC</sub> = Min                                                                     |                      |         |      |                 |      |

| I <sub>LOAD</sub> ≤ 1.6 mA                                                                                    | V <sub>OL</sub>      |         |      | Vss+.4          | v    |

| Output Low Current<br>(sinking)<br>VOL ≤ .4 V                                                                 | OL                   | 1.6     | ,    |                 | mA   |

| Supply Current Icc                                                                                            |                      |         | 110  | 150             | mA   |

#### PIN CONNECTIONS

| PIN | 6540            | 6541                     | PIN | 6540                       | 6541                       |

|-----|-----------------|--------------------------|-----|----------------------------|----------------------------|

| 1   | V <sub>ss</sub> | GND                      | 15  | A <sub>6</sub>             | A <sub>10</sub>            |

| 2   | cs <sub>5</sub> | <sup>A</sup> 0           | 16  | $\emptyset_2$              | DB <sub>7</sub>            |

| 3   | cs <sub>4</sub> | A <sub>3</sub>           | 17  | cs <sub>1</sub>            | DB <sub>6</sub>            |

| 4   | cs <sub>3</sub> | A <sub>4</sub>           | 18  | AIO                        | DB <sub>5</sub>            |

| 5   | A <sub>0</sub>  | A <sub>3</sub>           | 19  | DB <sub>7</sub>            | $DB_4$                     |

| 6   | A <sub>1</sub>  | A <sub>4</sub>           | 20  | DB <sub>6</sub>            | DB <sub>3</sub>            |

| 7   | $A_2$           | A <sub>5</sub>           | 21  | DB <sub>5</sub>            | $DB_2$                     |

| 8   | $A_3$           | A <sub>9</sub>           | 22  | $DB_4$                     | $^{\mathrm{DB}}$ 1         |

| 9   | A <sub>4</sub>  | Vcc                      | 23  | $DB_3$                     | $^{\mathrm{DB}}\mathrm{o}$ |

| 10  | A <sub>5</sub>  | A <sub>8</sub>           | 24  | $^{\mathrm{DB}}2$          | GS <sub>2</sub>            |

| 11  | A <sub>9</sub>  | A <sub>7</sub>           | 25  | $DB_1$                     |                            |

| 12  | Vcc             | A <sub>6</sub>           | 26  | $^{\mathrm{DB}}\mathrm{o}$ |                            |

| 13  | A <sub>8</sub>  | $\overline{\emptyset_2}$ | 27  | cs <sub>2</sub>            |                            |

| 14  | A <sub>7</sub>  | $cs_1$                   | 28  | N.C.                       |                            |

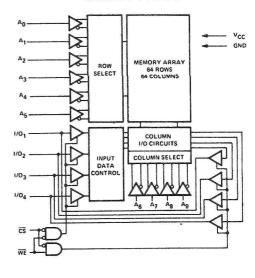

# 1024x4 Static Random Access Memory

SY2114

## MEMORY PRODUCTS

- 300 ns Maximum Access

- Low Operating Power Dissipation 0.1 mW/Bit

- No Clocks or Strobes Required

- Identical Cycle and Access Times

- Single +5V Supply

- Totally TTL Compatible:

All Inputs, Outputs, and Power Supply

- Common Data I/O

- 400 mv Noise Immunity

- High Density 18 Pin Package

The SY2114 is a 4096-Bit static Random Access Memory organized 1024 words by 4-bits and is fabricated using Synertek's N-channel Silicon-Gate MOS technology. It is designed using fully DC stable (static) circuitry in both the memory array and the decoding and therefore requires no clock or refreshing to operate. Address setup times are not required and the data is read out nondestructively with the same polarity as the input data. Common Input/Output pins are provided to simplify design of the bus oriented systems, and can drive 2 TTL loads.

The SY2114 is designed for memory applications where high performance, low cost, large bit storage, and simple interfacing are important design objectives. It is totally TTL compatible in all respects: inputs, outputs, and the single +5V supply. A separate Chip Select (CS) input allows easy selection of an individual device when outputs are or-tied.

The SY2114 is packaged in an 18-pin DIP for the highest possible density and is fabricated with N-channel, Ion Implanted, Silicon-Gate technology — a technology providing excellent performance characteristics as well as protection against contamination allowing the use of low cost packaging techniques.

#### PIN CONFIGURATION

#### ORDERING INFORMATION

| Order<br>Number | Package<br>Type | Access<br>Time | Supply<br>Current<br>(Max) | Temperature<br>Range |

|-----------------|-----------------|----------------|----------------------------|----------------------|

| SYC2114         | Ceramic         | 450nsec        | 100mamp                    | 0°C to 70°C          |

| SYP2114         | Molded          | 450nsec        | 100mamp                    | 0°C to 70°C          |

| SYC2114-3       | Ceramic         | 300nsec        | 100mamp                    | 0°C to 70°C          |

| SYP2114-3       | Molded          | 300nsec        | 100mamp                    | 0°C to 70°C          |

| SYC2114L        | Ceramic         | 450nsec        | 70mamp                     | 0°C to 70°C          |

| SYP2114L        | Molded          | 450nsec        | 70mamp                     | 0°C to 70°C          |

| SYC2114L-3      | Ceramic         | 300nsec        | 70mamp                     | 0°C to 70°C          |

| SYP2114L-3      | Molded          | 300nsec        | 70mamp                     | 0°C to 70°C          |

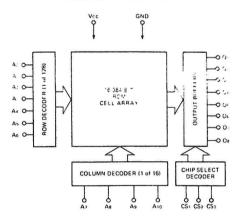

#### **BLOCK DIAGRAM**

Synertek®

P.O. Box 552

Santa Clara, CA 95052

Telephone (408) 984-8900

TWX: 910-338-0135

#### **ABSOLUTE MAXIMUM RATINGS**

Temperature Under Bias Storage Temperature

Voltage on Any Pin with

Respect to Ground Power Dissipation -10°C to 80°C -65°C to 150°C

-0.5V to +7V 1.0W

#### COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### D.C. CHARACTERISTICS T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = 5V ±5% (Unless Otherwise Specified)

|        |                                        | 2114- | 3, 2114 | 2114L, | 2114L-3 |      |                                              |

|--------|----------------------------------------|-------|---------|--------|---------|------|----------------------------------------------|

| Symbol | Parameter                              | Min   | Max     | Min    | Max     | Unit | Conditions                                   |

| ILI    | Input Load Current<br>(All input pins) |       | 10      |        | 10      | μА   | V <sub>IN</sub> = 0 to 5.25V                 |

| ILO    | I/O Leakage Current                    | 1     | 10      |        | 10      | μА   | <del>CS</del> = 2.0∨,                        |

|        |                                        |       | ks      |        |         |      | V <sub>I</sub> /O = 0.4V to V <sub>C</sub> C |

| ICC1   | Power Supply Current                   |       | 95      |        | 65      | mA   | VCC = 5.25V, II/O = 0 mA,                    |

|        |                                        |       | 1       |        |         |      | TA = 25°C                                    |

| ICC2   | Power Supply Current                   |       | 100     |        | 70      | mA   | VCC = 5.25V, II/O = 0 mA,                    |

|        |                                        |       |         |        |         |      | TA = 0°C                                     |

| VIL    | Input Low Voltage                      | -0.5  | 0.8     | -0.5   | 0.8     | V    |                                              |

| VIH    | Input High Voltage                     | 2.0   | Vcc     | 2.0    | Vcc     | V    |                                              |

| VOL    | Output Low Voltage                     |       | 0.4     |        | 0.4     | V    | IOL = 3.2 mA                                 |

| VOH    | Output High Voltage                    | 2.4   | Vcc     | 2.4    | Vcc     | V    | IOH = -1.0 mA                                |

#### CAPACITANCE TA = 25°C, f = 1.0 MHz

| Symbol | Test                     | Тур | Max | Units |

|--------|--------------------------|-----|-----|-------|

| C1/O   | Input/Output Capacitance |     | 5   | pF    |

| CIN    | Input Capacitance        |     | 5   | pF    |

NOTE: This parameter is periodically sampled and not 100% tested.

#### A.C. CHARACTERISTICS TA = 0°C to 70°C, VCC = 5V ±5% (Unless Otherwise Specified)

|                 |                                 | 2114-3 | 2114-3,2114L-3 |     | 2114, 2114L |      |

|-----------------|---------------------------------|--------|----------------|-----|-------------|------|

| SYMBOL          | PARAMETER                       | MIN    | MAX            | MIN | MAX         | UNIT |

| READ CYCLE      |                                 |        |                |     |             |      |

| tRC             | Read Cycle Time                 | 300    |                | 450 | 1 1         | nsec |

| tΑ              | Access Time                     |        | 300            |     | 450         | nsec |

| tCO             | Chip Select to Output Valid     |        | 100            |     | 120         | nsec |

| tCX             | Chip Select to Output Enabled   | 20     |                | 20  |             | nsec |

| tOTD            | Chip Deselect to Output Off     | 0      | 80             | 0   | 100         | nsec |

| tOHA            | Output Hold From Address Change | 50     |                | 50  |             | nsec |

| WRITECYCLE      |                                 | İ      | İ              | İ   | i i         |      |

| twc             | Write Cycle Time                | 300    |                | 450 |             | nsec |

| tAW             | Address to Write Setup Time     | 0      |                | 0   |             | nsec |

| tW              | Write Pulse Width               | 150    |                | 200 |             | nsec |

| tWR             | Write Release Time              | 0      |                | 0   |             | nsec |

| totw            | Write to Output Off             | 0      | 80             | 0   | 100         | nsec |

| tDW             | Data to Write Overlap           | 150    |                | 200 |             | nsec |

| <sup>t</sup> DH | Data Hold                       | 0      |                | 0   |             | nsec |

#### A.C. Test Conditions

| Input Pulse Levels               | V  |

|----------------------------------|----|

| Input Rise and Fall Time         | 00 |

| Timing Measurement Levels: Input | V  |

| Output                           |    |

| Output Load                      | F  |

## 12048x8 Static Read Only Memory SY2316B

# SY2316A

#### **MEMORY PRODUCTS**

- 2048x8 Bit Organization

- Single +5 Volt Supply

- Metal Mask Programming

- Two Week Prototype Turnaround

- Access Time-550ns /450ns (max.)

- **Totally Static Operation**

- Completely TTL Compatible

- Three-State Outputs for Wire-OR Expansion

- Three Programmable Chip Selects

- SY2316A Replacement for Intel 2316A

- SY2316B Pin Compatible with 2708 EPROM

- Replacement for Two 2708s

The SY2316A and SY2316B high performance read only memories are organized 2048 words by 8 bits with access times of less than 550 ns and 450 ns. These ROMs are designed to be compatible with all microprocessor and similar applications where high performance, large bit storage and simple interfacing are important design considerations. These devices offer TTL input and output levels with a minimum of 0.4 Volt noise immunity in conjunction with a +5 Volt power supply.

The SY2316A/B operate totally asynchronously. No clock input is required. The three programmable Chip Select inputs allow eight 16K ROMs to be OR-tied without external decoding. Both devices offer threestate output buffers for memory expansion.

Designed to replace two 2708 8K EPROMs, the SY2316B can eliminate the need to redesign printed circuit boards for volume mask programmed ROMs after prototyping with EPROMs.

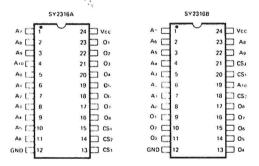

#### PIN CONFIGURATION

#### **BLOCK DIAGRAM**

#### ORDERING INFORMATION

| Order<br>Number | Package<br>Type | Access<br>Time | Temperature<br>Range             |

|-----------------|-----------------|----------------|----------------------------------|

| SYC2316A        | Ceramic         | 550ns          | $0^{\circ}$ C to $+70^{\circ}$ C |

| SYP2316A        | Plastic         | 550ns          | 0°C to +70°C                     |

| SYC2316B        | Ceramic         | 450ns          | $0^{\circ}$ C to $+70^{\circ}$ C |

| SYP2316B        | Plastic         | 450ns          | $0^{\circ}C$ to $+70^{\circ}C$   |

A custom number will be assigned by Synertek.

P.O. Box 552

Santa Clara, CA 95051

Telephone (408) 984-8900

TWX: 910-338-0135

B-10K-7/76

#### **ABSOLUTE MAXIMUM RATINGS\***

Ambient Operating Temperature 0° to +70°C

Storage Temperature -65°C to +150°C

Supply Voltage to Ground Potential -0.5V to +7.0V

Applied Output Voltage -0.5V to +7.0V

Applied Input Voltage -0.5V to +7.0V

Power Dissipation 1.0W

#### **COMMENT\***

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. CHARACTERISTICS

TA = 0°C to +70°C, Vcc = 5.0V ± 5% (unless otherwise specified)

| Symbol | Parameter              | Min. | Max. | Units | Test Conditions                    |

|--------|------------------------|------|------|-------|------------------------------------|

| Vон    | Output HIGH Voltage    | 2.4  | Vcc  | Volts | $Vcc = 4.75V$ , $Ioh = -200 \mu A$ |

| Vol    | Output LOW Voltage     |      | 0.4  | Volts | Vcc = 4.75V, loL = 2.1 mA          |

| ViH    | Input HIGH Voltage     | 2.0  | Vcc  | Volts | 27 as 1970                         |

| VIL    | Input LOW Voltage      | -0.5 | 0.8  | Volts | See Note 1                         |

| LI     | Input Load Current     |      | 10   | uΑ    | Vcc = 5.25V, 0V ≤ Vin ≤ 5.25V      |

| ILO    | Output Leakage Current |      | 10   | uA    | Chip Deselected                    |

|        |                        |      |      |       | Vout = +0.4V to Vcc                |

| lcc    | Power Supply Current   |      | 98   | mA    | Output Unloaded                    |

|        |                        |      |      |       | Vcc = 5,25V, Vin = Vcc             |

Note 1: Input levels that swing more negative than -0.5V will be clamped and may cause damage to the device.

#### A.C. CHARACTERISTICS

$T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{CC} = 5.0V \pm 5\%$  (unless otherwise specified)

|             |                                                   | SY2316B |      | SY2316A |      | 11.3  | 7 . 0 . 100                                                      |  |

|-------------|---------------------------------------------------|---------|------|---------|------|-------|------------------------------------------------------------------|--|

| Symbol      | Parameter                                         | Min.    | Max. | Min.    | Max. | Units | Test Conditions                                                  |  |

| tacc        | Address Access Time                               |         | 450  |         | 550  | ns    | Output load: 1 TTL load                                          |  |

| tco         | Chip Select Delay                                 |         | 250  |         | 300  | ns    | and 100 pf                                                       |  |

| <b>t</b> DF | Chip Deselect Delay                               |         | 250  |         | 300  | ns    | Input transition time: 20ns                                      |  |

| tон         | Previous Data Valid After<br>Address Change Delay | 20      |      | 20      |      | ns    | Timing reference levels:<br>Input: 1.5V<br>Output: 0.8V and 2.2V |  |

#### CAPACITANCE

ta = 25°C, f = 1.0MHz, See Note 2

| Symbol | Parameter          | Min. | Max. | Units | Test Conditions           |

|--------|--------------------|------|------|-------|---------------------------|

| Cı     | Input Capacitance  |      | 7    | pF    | All pins except pin under |

| Co     | Output Capacitance |      | 10   | pF    | test tied to AC ground    |

Note 2: This parameter is periodically sampled and is not 100% tested.

# ADDRESS INVALID VALID INVALID CHIP SELECT INPUTS DATA OUTPUTS HIGH IMPEDANCE TACC TIMING DIAGRAM INVALID INVALID INVALID VALID INVALID VALID INVALID HIGH IMPEDANCE

# TYPES SN54LS138, SN54LS139, SN54S138, SN54S139, SN74LS138, SN74LS139, SN74S138, SN74S139 DECODERS/DEMULTIPLEXERS

BULLETIN NO. DL-S 7611804, DECEMBER 1972-REVISED OCTOBER 1976

- Designed Specifically for High-Speed: Memory Decoders

Data Transmission Systems

- 'S138 and 'LS138 3-to-8-Line Decoders Incorporate 3 Enable Inputs to Simplify Cascading and/or Data Reception

- 'S139 and 'LS139 Contain Two Fully Independent 2-to-4-Line Decoders/ Demultiplexers

- Schottky Clamped for High Performance

| TYPE   | TYPICAL PROPAGATION DELAY (3 LEVELS OF LOGIC) | TYPICAL POWER DISSIPATION |

|--------|-----------------------------------------------|---------------------------|

| 'LS138 | 22 ns                                         | 32 mW                     |

| 'S138  | 8 ns                                          | 245 mW                    |

| 'LS139 | 22 ns                                         | 34 mW                     |

| 'S139  | 7.5 ns                                        | 300 mW                    |

|        |                                               |                           |

#### description

These Schottky-clamped TTL MSI circuits are designed to be used in high-performance memory-decoding or data-routing applications requiring very short propagation delay times. In high-performance memory systems these decoders can be used to minimize the effects of system decoding. When employed with high-speed memories utilizing a fastenable circuit the delay times of these decoders and the enable time of the memory are usually less than the typical access time of the memory. This means that the effective system delay introduced by the Schottky-clamped system decoder is negligible.

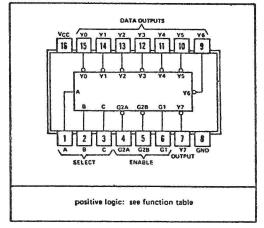

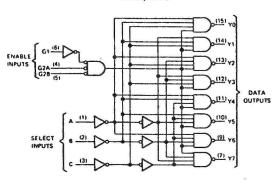

The 'LS138 and 'S138 decode one-of-eight lines dependent on the conditions at the three binary select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.

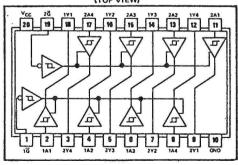

SN54LS138, SN54S138 ... J OR W PACKAGE SN74LS138, SN74S138 ... J OR N PACKAGE (TOP VIEW)

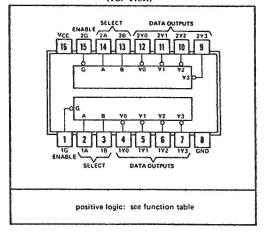

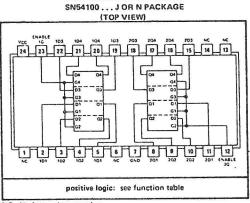

SN54LS139, SN54S139 ... J OR W PACKAGE SN74LS139, SN74S139 ... J OR N PACKAGE (TOP VIEW)

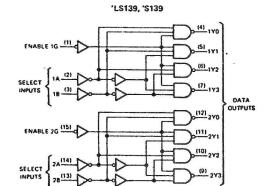

The 'LS139 and 'S139 comprise two individual two-line-to-four-line decoders in a single package. The active-low enable input can be used as a data line in demultiplexing applications.

All of these decoders/demultiplexers feature fully buffered inputs each of which represents only one normalized Series 54LS/74LS load ('LS138, 'LS139) or one normalized Series 54S/74S load ('S138, 'S139) to its driving circuit. All inputs are clamped with high-performance Schottky diodes to suppress line-ringing and simplify system design. Series 54LS and 54S devices are characterized for operation over the full military temperature range of --55°C to 125°C; Series 74LS and 74S devices are characterized for 0°C to 70°C industrial systems.

#### TYPES SN54LS138, SN54S138, SN54LS139, SN54S139 SN74LS138, SN74S138, SN74LS139, SN74S139 DECODERS/DEMULTIPLEXERS

#### functional block diagrams and logic

'LS138, 'S138

'LS138, 'S138 FUNCTION TABLE

|     | INPUTS |   |      |     | OUTPUTS |     |     |     |     |    |    |    |

|-----|--------|---|------|-----|---------|-----|-----|-----|-----|----|----|----|

| ENA | BLE    | S | ELEC | T   |         |     | ,   | 101 | PUI | 5  |    |    |

| G1  | G2°    | C | В    | A   | YO      | Y1  | Y2  | Y3  | Y4  | V5 | Y6 | Y7 |

| X   | Н      | X | ×    | ×   | Н       | Н   | Н   | Н   | Н   | н  | Н  | Н  |

| L   | X      | × | X    | X   | H       | H   | H   | H   | H   | H  | H  | н  |

| H   | L      | L | L    | L   | L       | Н   | H   | Н   | H   | H  | H  | н  |

| H   | L      | L | L    | Н   | н       | L   | H   | Н   | H   | H  | H  | Н  |

| н   | L      | L | н    | L   | н       | H   | L   | Н   | H   | Н  | H  | 14 |

| H   | L      | L | H    | н   | Н       | 1   | Н   | L   | H   | Н  | H  | H  |

| H   | L      | н | L    | L   | н       | 8-9 | н   | H   | L   | H  | H  | H  |

| Н   | L      | н | L    | н   | н       | Н   | 8-4 | Н   | Н   | L  | H  | Н  |

| н   | L      | н | н    | L   | н       | H   | н   | H   | Н   | 14 | L  | H  |

| н   | L      | н | н    | 8-8 | н       | Н   | н   | H   | Н   | H  | н  | L  |

\*G2 = G2A + G2B H = high level, L = low level, X = irrelevant

'LS139, 'S139 (EACH DECODER/DEMULTIPLEXER) FUNCTION TABLE

| INP    | 011701170       |   |         |    |    |    |

|--------|-----------------|---|---------|----|----|----|

| ENABLE | ENABLE   SELECT |   | OUTPUTS |    |    |    |

| G      | В               | A | YO      | Y1 | Y2 | Y3 |

| Н      | X               | X | Н       | H  | Н  | Н  |

| L      | L               | L | L       | H  | H  | H  |

| L      | L               | Н | Н       | L  | H  | Н  |

| L      | н               | L | н       | Н  | L  | H  |

| Ĺ      | Н               | H | Н       | H  | H  | L  |

H = high level, L = low level, X = irrelevent

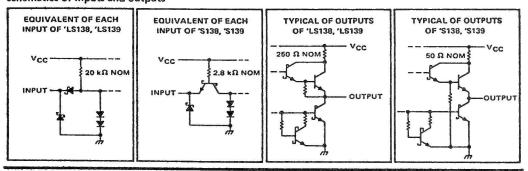

#### schematics of inputs and outputs

J

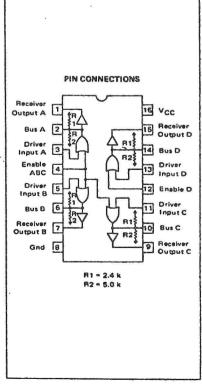

| Device | Temperature Range | Package     |

|--------|-------------------|-------------|

| MC3446 | 0°C to +70°C      | Plastic DIP |

MC3446

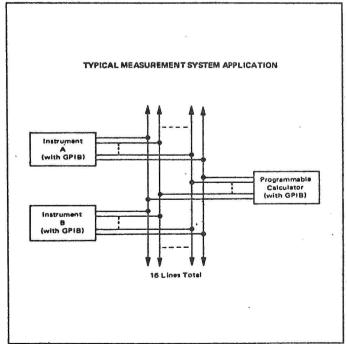

#### QUAD GENERAL PURPOSE INTERFACE BUS (G.P.I.B.) TRANSCEIVER

The MC3446 is a quad bus transceiver intended for usage in instruments and programmable calculators equipped for interconnection into complete measurement systems. This transceiver allows the bidirectional flow of digital data and commands between the various instruments. The transceiver provides four open-collector drivers and four receivers featuring hysteresis.

- Tailored to Meet the IEEE Standard 488-1975 (Digital Interface for Programmable Instrumentation) and the Proposed IEC Standard on Instrument Interface

- Provides Electrical Compatibility with Hewlett Packard Interface Bus. (HP-IB)

- MOS Compatible with High Impedance Inputs

- Driver Output Guaranteed Off During Power Up/Power Down

- Low Power Average Power Supply Current = 12 mA

- Termination Resistors Provided

QUAD INTERFACE BUS TRANSCEIVER SILICON MONOLITHIC INTEGRATED CIRCUIT

P SUFFIX PLASTIC PACKAGE CASE 648

5.

| ARA VIRGIBA DA TIRIC | C 17 - 250 | C unlace asharmic | I basen a |

|----------------------|------------|-------------------|-----------|

| Reting                              | Symbol | Value       | Unit |

|-------------------------------------|--------|-------------|------|

| Power Supply Voltage                | Vcc    | 7.0         | Vds  |

| Input Voltage                       | Vı     | 5.5         | Vdc  |

| Driver Output Current               | 10(0)  | 150         | mA   |

| Junction Temperature                | TJ     | 150         | °C   |

| Operating Ambient Temperature Range | TA     | 0 to +70    | °C   |

| Storage Temperature Range           | Tsto   | -65 to +150 | oc   |

ELECTRICAL CHARACTERISTICS (Unless otherwise noted, 4 75 V <  $V_{CC}$  < 5.25 V and 0 <  $T_A$  <  $70^{\circ}$ C, typical values are at  $T_A = 25^{\circ}$ C.  $V_{CC} = 5.0$  V)

|                                                                     | TA = 25°C, VCC = 5.0 V)                                                                                                                        |         |                  | 24.7     |             |           |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|----------|-------------|-----------|

| Char                                                                | Symbol                                                                                                                                         | Min     | Тур              | Max      | Unit        |           |

| DRIVER PORTION                                                      |                                                                                                                                                |         |                  |          |             |           |

| Input Voltage - High Logic State                                    |                                                                                                                                                | VIH(D)  | 2.0              |          | -           | V         |

| Input Voltage - Low Logic State                                     |                                                                                                                                                | VIL(D)  |                  | -        | 8.0         | V         |

| Input Current - High Logic State<br>(VIH = 2.4 V)                   |                                                                                                                                                | liH(D)  | -                | 5.0      | 20          | μА        |

| Input Current - Low Lagic State<br>{VIL = 0.4 V, VCC = 5.0 V, TA    | = 25°C1                                                                                                                                        | liL(D)  | -                | 0.2      | 0.36        | mA        |

| Input Clamp Voltage<br>(I <sub>I</sub> C = -12 mA)                  |                                                                                                                                                | VIC(D)  | -                | -        | -1.5        | V         |

| Output Voltage - High Logic State<br>(VIH(S) = 2.4 V or V(H(D) = 2. |                                                                                                                                                | AOH(D)  | 2.5              | 3.3      | 3.7         | V         |

| Output Voltage - Low Logic State<br>(VIL(S) = 0 8 V. VIL(D) = 0.8 V |                                                                                                                                                | VOL(D)  | -                | -        | 0.4         |           |

| Input Breakdown Current<br>(V <sub>1</sub> (D) = 5.5 V)             | IB(D)                                                                                                                                          | -       | -                | 1.0      | mA          |           |

| RECEIVER PORTION                                                    |                                                                                                                                                |         |                  |          |             |           |

| Input Hysteresis                                                    | -                                                                                                                                              | 400     | 900              | -        | mV          |           |

| Input Threshold Voltage - Low to                                    | VILH(R)                                                                                                                                        | -       | 1.78             | 2.0      | V           |           |

| Input Threshold Voltage - High to                                   | Low Output Logic State                                                                                                                         | VIHL(R) | 0.6              | 0.88     | -           | V         |

| Output Voltage - High Logic State<br>(VIH(R) * 2.0 V. IOH(R) * -40  |                                                                                                                                                | VOH(R)  | 2.4              | -        | -           | V         |

| Output Voltage - Low Logic State<br>(VIL(R) = 08 V. IOL(R) = 80     |                                                                                                                                                | VOLIRI  | -                | -        | 0.4         | ٧         |

| Output Short-Circuit Current<br>(V1H(R) = 2.0 V) (Only one ou       | put may be shorted at a time)                                                                                                                  | los(R)  | 4.0              | -        | 14          | mA        |

| BUS LOAD CHARACTERISTICS                                            |                                                                                                                                                |         |                  |          |             | NOTE SAID |

| Bus Voltage                                                         | (V <sub>IH(E)</sub> = 2.4 V)<br>(I <sub>BUS</sub> = -12 mA)                                                                                    | V(BUS)  | 2.5              | 3.3<br>- | 3.7<br>-1.5 | V         |

| Bus Current                                                         | (V <sub>IH</sub> (0)= 2.4 V, V <sub>BUS</sub> > 50 V)<br>(V <sub>IH</sub> (D) = 2.4 V, V <sub>BUS</sub> = 0.4 V)<br>(V <sub>BUS</sub> < 5.5 V) | (BUS)   | 0.7<br>-1.3<br>- | -        | -3 2<br>2.5 | mA        |

| TOTAL DEVICE POWER CONSU                                            | MPTION                                                                                                                                         |         |                  |          |             |           |

| Power Supply Current (All Drivers OFF) (All Drivers ON)             | Icc                                                                                                                                            | _       | 12<br>32         | 19<br>39 | mA          |           |

#### SWITCHING CHARACTERISTICS (VCC = 5.0 V. TA = 25°C)

| Characteristic                                                            | Symbol  | Min | Тур | Max | Unit |

|---------------------------------------------------------------------------|---------|-----|-----|-----|------|

| DRIVER PORTION                                                            |         |     |     |     |      |

| Propagation Delay Time from Driver Input to Low Logic State Bus Output    | TPHL(D) | -   | 34  | 50  | ns   |

| Propagation Delay Time from Driver Input to High Logic State Bus Output   | tPLH(D) | -   | 17  | 40  | ns   |

| Propagation Delay Time from Enable Input to Low Logic State Bus Output    | PHL(E)  | -   | 39  | 50  | ns.  |

| Propagation Delay Time from Enable Input to High Logic State Bus Output   | 1PLH(E) | -   | 32  | 50  | ns.  |

| RECEIVER PORTION                                                          |         |     |     |     |      |

| Propagation Delay Time from Bus Input to High Logic State Receiver Output | TPLH(R) | -   | 37  | 50  | ns   |

| Propagation Dalay Time from Bus Input to Low Logic State Receiver Output  | PHL(R)  | -   | 22  | 40  | ns   |

MOTOROLA Semiconductor Products Inc. -

# Synertek

5

3050 Coronado Drive, Santa Clara, CA. 95051 (408) 984-8900 TWX 910-338-0135 SY6500

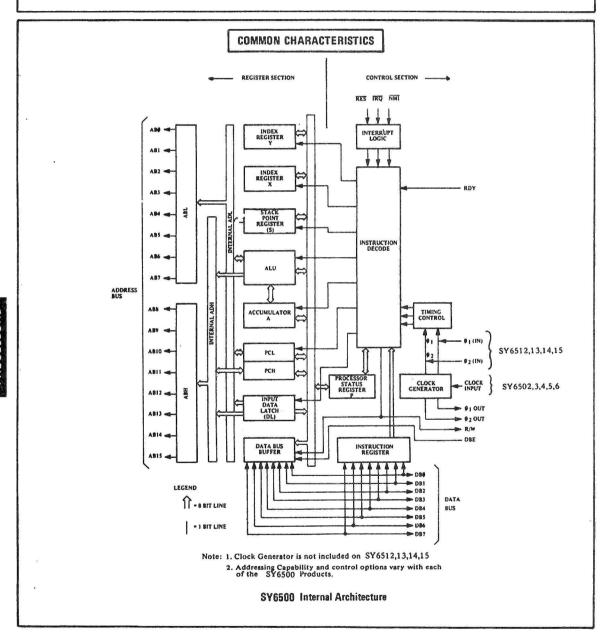

#### SY6500 MICROPROCÈSSORS

#### The SY6500 Microprocessor Family Concept ----

The SY6500 Series Microprocessors represent the first totally software compatible microprocessor family. This family of products includes a range of software compatible microprocessors which provide a selection of addressable memory range, interrupt input options and on-chip clock osscillators and drivers. All of the microprocessors in the SY6500 group are software compatible within the group and are bus compatible with the M6800 product offering.

The family includes five microprocessors with on-board clock oscillators and drivers and four microprocessors driven by external clocks. The on-chip clock versions are aimed at high performance, low cost applications where single phase inputs, crystal or RC inputs provide the time base. The external clock versions are geared for the multi processor system applications where maximum timing control is mandatory. All versions of the microprocessors are available in 1 MHz and 2 MHz ("A" suffix on product numbers) maximum operating frequencies.

#### Features of the SY6500 Family

- . Single five volt supply

- . N channel, silicon gate, depletion load technology

- . Eight bit parallel processing

- . 56 Instructions

- . Decimal and binary arithmetic

- . Thirteen addressing modes

- . True indexing capability

- . Programmable stack pointer

- . Variable length stack

- . Interrupt capability

- . Non-maskable interrupt

- . Use with any type or speed memory

- . Bi-directional Data Bus

- . Instruction decoding and control

- . Addressable memory range of up to 65K bytes

- . "Ready" input

- . Direct memory access capability

- . Bus compatible with MC6800

- . Choice of external or on-board clocks

- . 1MHz and 2MHz operation

- . On-the-chip clock options

- \* External single clock input

- \* RC time base input

- \* Crystal time base input

- . 40 and 28 pin package versions

- . Pipeline architecture

#### SY6502 - 40 Pin Package

| - Allegarett i der |                                                                                                                                                                                                                                                    |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 40- RES          |                                                                                                                                                                                                                                                    |

| 2 39- 021001       | ')                                                                                                                                                                                                                                                 |

| 3 38 - S.O.        |                                                                                                                                                                                                                                                    |

| 4 37 - 00(IN)      |                                                                                                                                                                                                                                                    |

| 5 36 - N.C.        |                                                                                                                                                                                                                                                    |

| 6 35 - N. C.       |                                                                                                                                                                                                                                                    |

| 7 34-R/W           |                                                                                                                                                                                                                                                    |

| 8 33 - DBO         |                                                                                                                                                                                                                                                    |

| 9 32 DBI           |                                                                                                                                                                                                                                                    |

|                    |                                                                                                                                                                                                                                                    |

| 11 30-0B3          |                                                                                                                                                                                                                                                    |

|                    |                                                                                                                                                                                                                                                    |

|                    |                                                                                                                                                                                                                                                    |

| 14 27-DB6          |                                                                                                                                                                                                                                                    |

| 15 26-087          |                                                                                                                                                                                                                                                    |

| 16 25 - AB15       |                                                                                                                                                                                                                                                    |

| 17 24- ABI4        |                                                                                                                                                                                                                                                    |

| 18 23 - ABI3       |                                                                                                                                                                                                                                                    |

| 19 22- AB12        |                                                                                                                                                                                                                                                    |

| 20 21 - Vas        |                                                                                                                                                                                                                                                    |

| SY6502             |                                                                                                                                                                                                                                                    |

|                    | 2 39 - @g(OUT<br>30 - S(O.)<br>4 37 - @g(IN)<br>5 36 - N. C.<br>7 34 - R/W<br>9 32 - D81<br>10 31 - D82<br>11 30 - D83<br>12 29 - D84<br>11 20 - D85<br>14 27 - D86<br>15 26 - D87<br>16 25 - A815<br>17 24 - A814<br>18 23 - A815<br>19 22 - A812 |

- \* 65K Addressable Bytes of Memory

- \* IRQ Interrupt

- \* NMI Interrupt

- \* On-the-chip Clock

- ✓ TTL Level Single Phase Input

- ✓ RC Time Base Input

- √ Crystal Time Base Input

- \* SYNC Signal

(can be used for single instruction

- execution)

\* RDY Signal

- (can be used for single cycle execution)

- \* Two Phase Output Clock for Timing of Support Chips

Features of SY6502

#### Comments on the Data Sheet

The data sheet is constructed to review first the basic "Common Characteristics" - those features which are common to the general family of microprocessors. Subsequent to a review of the family characteristics will be sections devoted to each member of the group with specific features of each.

## 5

3050 Coronado Drive, Santa Clara, CA. 95051 (408) 984-8900 TWX 910-338-0135

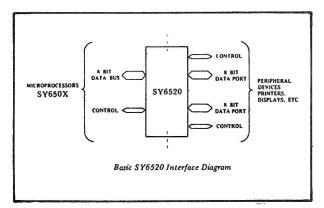

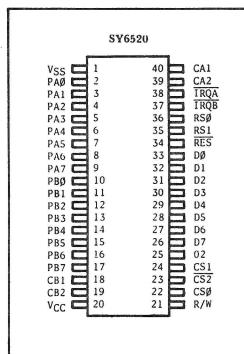

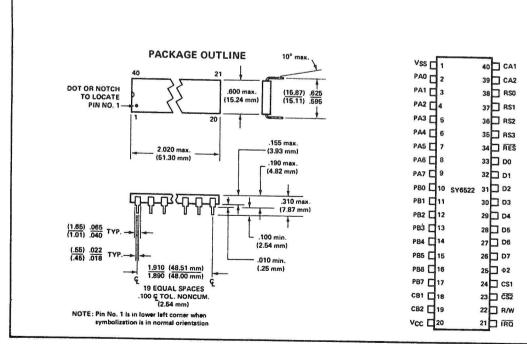

#### SY6520 PERIPHERAL ADAPTER

#### DESCRIPTION

The SY6520 Peripheral Adapter is designed to solve a broad range of peripheral control problems in the implementation of microcomputer systems. This device allows a very effective trade-off between software and hardware by providing significant capability and flexibility in a low cost chip. When coupled with the power and speed of the SY6500 family of microprocessors, the SY6520 allows implementation of very complex systems at a minimum overall cost.

Control of peripheral devices is handled primarily through two 8-bit bi-directional ports. Each of these lines can be programmed to act as either an input or an output. In addition, four peripheral control/interrupt input lines are provided. These lines can be used to interrupt the processor or for "hand-shaking" data between the processor and a peripheral device.

- High performance replacement for Motorola/AMI/MOSTEK/Hitachi peripheral adapter.

- N channel, depletion load technology, single +5V supply.

- · Completely Static and TTL compatible.

- · CMOS compatible peripheral control lines.

- Fully automatic "hand-shake" allows very positive control of data transfers between processor and peripheral devices.

MICRO. PROCESSORS

#### SUMMARY OF SY6520 OPERATION

See SYNERTEK Microcomputer Hardware Manual for detailed description of SY6520 operation.

|       |                                                                                                                                                             |                                       | CA1/CBI CONTROL                                                                           |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------|--|--|

|       | Bit 0                                                                                                                                                       | Active Transition<br>of Input Signal* | IRQA (IRQB) Interrupt Outputs                                                             |  |  |

| 0     | 0                                                                                                                                                           | negative                              | Disableremain high                                                                        |  |  |

| 0     | 1                                                                                                                                                           | negative                              | Enablegoes low when bit 7 in CRA (CRB) is set by active transition of signal on CA1 (CB1) |  |  |

| 1     | 0                                                                                                                                                           | positive                              | Disableremain high                                                                        |  |  |

| 1     | 1                                                                                                                                                           | positive                              | Enableas explained above                                                                  |  |  |

| *Note | *Note: Bit 7 of CRA (CRB) will be set to a logic 1 by an active transition of the CA1 (CB1) signal. This is independent of the state of Bit 0 in CRA (CRB). |                                       |                                                                                           |  |  |

| C      | RA (CRB | ` | CA2/CB2                               | INPUT MODES                                                                               |

|--------|---------|---|---------------------------------------|-------------------------------------------------------------------------------------------|

|        | Bit 4   | - | Active Transition<br>of Input Signal* | IRQA (IRQB)<br>Interrupt Output                                                           |

| 0      | 0       | 0 | negative                              | Disableremains high                                                                       |

| 0      | 0       | 1 | negative                              | Enablegoes low when bit 6 in CRA (CRB) is set by active transition of signal on CA2 (CB2) |

| 0      | 1       | 0 | positive                              | Disableremains high                                                                       |

| 0      | 1       | 1 | positive                              | Enableas explained above                                                                  |

| *Note: |         |   |                                       | a logic $l$ by an active transition of the CA2 (CB2) he state of Bit $3$ in CRA (CRB).    |

|       | CRA   |       | CA                     | 2 OUTPUT MODES                                                                                                                                                                                                                      |

|-------|-------|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 5 | Bit 4 | Bit 3 | Mode                   | Description                                                                                                                                                                                                                         |

| 1     | 0     | 0     | "Handshake"<br>on Read | CA2 is set high on an active transition of the CA1 interrupt input signal and set low by a microprocessor "Read A Data" operation. This allows positive control of data transfers from the peripheral device to the microprocessor. |

| 1     | 0     | 1     | Pulse Output           | CA2 goes low for one cycle after a "Read A Data" operation. This pulse can be used to signal the peripheral device that data was taken.                                                                                             |

| 1     | 1     | 0     | Manual Output          | CA2 set low                                                                                                                                                                                                                         |

| 1     | 1     | 1     | Manual Output          | CA2 set high                                                                                                                                                                                                                        |

|   | CB2 OUTPUT MODES |       |       |                         |                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|---|------------------|-------|-------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|   |                  | CRB   |       |                         |                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|   | Bit 5            | Bit 4 | Bit 3 | Mode                    | Description                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|   | 1                | 0     | 0     | "Handshake"<br>on Write | CB2 is set low on microprocessor "Nrite B Data" operation and is set high by an active transition of the CB1 interrupt input signal. This allows positive control of data transfers from the microprocessor to the peripheral device. |  |  |  |  |  |  |  |  |  |

|   | 1                | 0     | 1     | Pulse Output            | CB2 goes low for one cycle after a microprocessor 'Write B<br>Data" operation. This can be used to signal the peripheral<br>device that data is available.                                                                            |  |  |  |  |  |  |  |  |  |

| l | 1                | 1     | 0     | Manual Output           | CB2 set low                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|   | 1                | 1     | 1     | Manual Output           | CB2 set high                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

MICRO.

# Synertek

5

3050 Coronado Drive, Santa Clara, CA. 95051 (408) 984-8900 TWX 910-338-0135 SY6522

#### SY6522 (VERSATILE INTERFACE ADAPTER)

The SY6522 Versatile Interface Adapter (VIA) provides all of the capability of the SY6520. In addition, this device contains a pair of very powerful interval timers, a serial-to-parallel/parallel-to-serial shift register and input data latching on the peripheral ports. Expanded handshaking capability allows control of bi-directional data transfers between VIA's in multiple processor systems.

Control of peripheral devices is handled primarily through two 8-bit bi-directional ports. Each of these lines can be programmed to act as either an input or an output. Also, several peripheral I/O lines can be controlled directly from the interval timers for generating programmable frequency square waves and for counting externally generated pulses. To facilitate control of the many powerful features of this chip, the internal registers have been organized into an interrupt flag register, an interrupt enable register and a pair of function control registers.

- · Very powerful expansion of basic SY6520 capability.

- N channel, depletion load technology, single +5V Supply.

- · Completely static and TTL compatible.

- · CMOS compatible peripheral control lines.

- Expanded "handshake" capability allows very positive control of data transfers between processor and peripheral devices.

#### **MAXIMUM RATINGS**

This device contains circuitry to protect the inputs against damage due to high static voltages. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages.

#### Electrical Characteristics (V<sub>CC</sub> = 5.0V $\pm$ 5%, V<sub>SS</sub> = 0, T<sub>A</sub> = 0°C to 70°C unless otherwise noted)

| CHARACTERISTIC                                                                                                                             | SYMBOL           | MIN          | TYP           | MAX        | UNIT         |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|---------------|------------|--------------|

| Input high voltage (normal operation)                                                                                                      | V <sub>IH</sub>  | +2.4         |               | Vcc        | Vdc          |

| Input Low Voltage (normal operation)                                                                                                       | VIL              | -0.3         | _             | +0.4       | Vdc          |

| Input Leakage current - V <sub>IN</sub> = 0 to 5 Vdc<br>R/W, RES, RS0, RS1, RS2, RS3, CS1,<br>CS2, CA1, Φ2                                 | IIN              | _            | ±1.0          | ±2.5       | μAdc         |

| Off-state input current - V <sub>IN</sub> = .4 to 2.4 V<br>Vcc = Max, D0 to D7                                                             | ITSI             | -            | ±2.0          | ±10        | μAdc         |

| Input high current - V <sub>IH</sub> = 2.4 V<br>PAO - PA7, CA2, PBO - PB7, CB1, CB2                                                        | IIH              | -100         | -250          | -          | μAdc         |

| Input low current - VIL = 0.4 Vdc PAO - PA7, CA2, PBO - PB7, CB1, CB2                                                                      | IIL              | -            | -1.0          | -1.6       | m Adc        |

| Output high voltage  Vcc = min, I <sub>load</sub> = -100 μAdc  PAO - PA7, CA2, PBO -PB7, CB1, CB2                                          | VOH              | 2.4          | -             | -          | Vdc          |

| Output low voltage  Vcc = min, I <sub>load</sub> = 1.6 mAdc                                                                                | Vol              | _            | -             | +0.4       | Vdc          |

| Output high current (sourcing)  VOH = 2.4 V  VOH = 1.5 V, PBO - PB7, CB1, CB2                                                              | IOH              | -100<br>-3.0 | -1000<br>-5.0 | _          | μAdc<br>mAdc |

| Output low current (sinking)  VOL = 0.4 Vdc                                                                                                | IOL              | 1.6          | -             | -          | mAdc         |

| Output leakage current (off state) IRQ                                                                                                     | I <sub>off</sub> | _            | 1.0           | 10         | μAdc         |

| Input capacitance - T <sub>A</sub> = 25°C, f = 1 Mhz<br>R/W, RES, RS0, RS1, RS2, RS3, CS1, CS2<br>DO - D7, PA0 - PA7, CA1, CA2, PB0 - PB7, | C <sub>in</sub>  | _            | _             | 7.0<br>10  | pF<br>pF     |

| CB1, CB2                                                                                                                                   |                  |              | _             | 75.000     |              |

| Φ2 input                                                                                                                                   | <del></del>      |              | -             | 20         | pF           |

| Output capacitance - TA = 25°C, f = 1 Mhz  Power dissipation                                                                               | C <sub>out</sub> |              | _             | 10<br>1000 | pF<br>MW     |

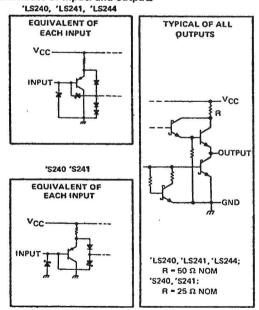

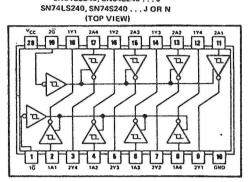

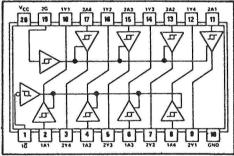

#### TYPES SN54LS240,SN54LS241,SN54LS244,SN54S240,SN54S241, SN74LS240,SN74LS241,SN74LS244,SN74S240,SN74S241 OCTAL BUFFERS AND LINE DRIVERS WITH 3-STATE OUTPUTS

|         | Typical<br>IOL<br>(Sink | Typical<br>IOH<br>(Source |           | Propagation<br>by Times | Typical<br>Enable/<br>Disable | Dis        | cal Power<br>sipation<br>abled) |

|---------|-------------------------|---------------------------|-----------|-------------------------|-------------------------------|------------|---------------------------------|

|         | Current)                | Current)                  | Inverting | Noninverting            | Times                         | Inverting  | Noninverting                    |

| SN54LS' | 12 mA                   | -12 mA                    | 10.5 ns   | 12 ns                   | 18 ns                         | 130 mW     | 135 mW                          |

| SN74LS' | 24 mA                   | -15 mA                    | 10.5 ns   | 12 ns                   | 18 ns                         | 130 mW     | 135 mW                          |

| SN545'  | 48 mA                   | -12 mA                    | 4.5 ns    | 6 ns                    | 9 ns                          | 450 mW     | 538 mW                          |

| SN74S'  | N74S' 64 mA -15 mA      |                           | 4.5 ns    | 6 ns                    | 9 ns                          | 450 mW     | 538 mW                          |

|         |                         |                           |           |                         | SN54L                         | S240, SN54 | S240 J                          |

- 3-State Outputs Drive Bus Lines or Buffer Memory Address Registers

- P-N-P Inputs Reduce D-C Loading

- Hysteresis at Inputs Improves Noise Margins

#### description

These octal buffers and line drivers are designed specifically to improve both the performance and density of three-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. The designer has a choice of selected combinations of inverting and noninverting outputs, symmetrical  $\overline{G}$  (active-low output control) inputs, and complementary G and  $\overline{G}$  inputs. These devices feature high fan-out, improved fan-in, and 400-mV noise-margin. The SN74LS' and SN74S' can be used to drive terminated lines down to 133 ohms.

#### schematics of inputs and outputs

SN54LS241, SN54S241 . . . J SN74LS241, SN74S241 . . . J OR N (TOP VIEW)

SN54LS244 ... J SN74LS244 ... J OR N (TOP VIEW)

#### TTL MSI

#### TYPES SN54100, SN74100 8-BIT BISTABLE LATCHES

BULLETIN NO. DL S 7211830, DECEMBER 1972

logic

#### FUNCTION TABLE

|   |               | /cacı | Laten |                  |

|---|---------------|-------|-------|------------------|

| Г | INPUTS<br>D G |       | OUT   | PUTS             |

|   | D             | G     | Q     | ã                |

| Γ | L             | н     | L     | Н                |

| 1 | H             | н     | н     | L                |

|   | X             | L     | 00    | $\bar{\alpha}_0$ |

H = high level, X = irrelevant

Q0 = the level of Q before the

high-to-low transition of G

#### description

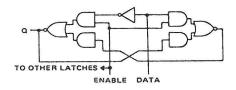

These latches are ideally suited for use as temporary storage for binary information between processing units and input/output or indicator units. Information present at a data (D) input is transferred to the Q output when the enable (G) is high and the Q output will follow the data input as long as the enable remains high. When the enable goes low, the information (that was setup at the data input at the time the transition occurred) is retained at the Q output until the enable is permitted to go high.

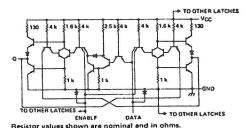

These circuits are completely compatible with all popular TTL or DTL families. All inputs are diodeclamped to minimize transmission-line effects and simplify system design. Typical power dissipation is 40 milliwatts per latch. The SN54100 is characterized for operation over the full military temperature range of -55° to 125°C; the SN74100 is characterized for operation from 0°C to 70°C.

SN54100 ... J OR W PACKAGE

NC-No internal connection

#### functional block diagram (each latch)

#### schematic (each latch)

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)              | . 7V     |

|-----------------------------------------------|----------|

| Input voltage                                 |          |

| Intermitter voltage (see Note 2)              | . 5.5 V  |

| Operating free-air temperature range: SN54100 | to 125°C |

| SN74100                                       | to 70°C  |

| Storage temperature range65°C                 | to 150°C |

NOTES: 1. Voltage values, except Interemitter voltage, are with respect to network ground terminal.

This is the voltage between two emitters of a multiple-emitter input transistor. For this circuit, this rating applies between the enable and D inputs of any latch.

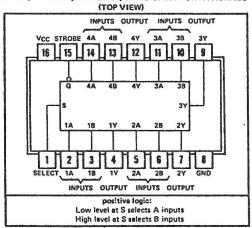

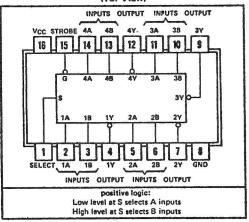

# TYPES SN54157, SN54L157, SN54LS157, SN54LS158, SN54S157, SN54S158, SN74157, SN74L157, SN74LS157, SN74LS158, SN74S157, SN74S158 QUADRUPLE 2-LINE-TO-1-LINE DATA SELECTORS/MULTIPLEXERS

BULLETIN NO. DL-S 7711847, MARCH 1974-REVISED AUGUST 1977

#### features

- Buffered Inputs and Outputs

- Three Speed/Power Ranges Available

| TYPES        | TYPICAL<br>AVERAGE<br>PROPAGATION<br>TIME | TYPICAL<br>POWER<br>DISSIPATION |

|--------------|-------------------------------------------|---------------------------------|

| 167          | 9 ns                                      | 150 mW                          |

| 'L157        | 18 ns                                     | 75 mW                           |

| 'LS157       | 9 ns                                      | 49 mW                           |

| <b>'S157</b> | 5 ns                                      | 250 mW                          |

| 'LS158       | 7 ns                                      | 24 mW                           |

| 'S158        | 4 ns                                      | 195 mW                          |

#### applications

- Expand Any Data Input Point

- Multiplex Dual Data Buses

- Generate Four Functions of Two Variables (One Variable Is Common)

- Source Programmable Counters

#### description

These monolithic data selectors/multiplexers contain inverters and drivers to supply full on-chip data selection to the four output gates. A separate strobe input is provided. A 4-bit word is selected from one of two sources and is routed to the four outputs. The '157, 'L157, 'LS157, and 'S157 present true data whereas the 'LS158 and 'S158 present inverted data to minimize propegation delay time.

FUNCTION TABLE

|        | INPU   | OUTPUT Y |   |                               |                         |  |  |  |  |  |

|--------|--------|----------|---|-------------------------------|-------------------------|--|--|--|--|--|

| STROBE | SELECT | A        | В | '157, 'L157,<br>'LS157,'\$157 | 'LS158<br>'81 <b>58</b> |  |  |  |  |  |

| Н      | ×      | X        | × | L                             | Н                       |  |  |  |  |  |

| L      | L      | . L      | × | L                             | н .                     |  |  |  |  |  |

| L      | L      | н        | × | н                             | L                       |  |  |  |  |  |

| L      | н      | ×        | L | L                             | Н                       |  |  |  |  |  |

| L      | н      | ×        | Н | н                             | L                       |  |  |  |  |  |

H = high level, L = low level, X = irrelevant

SN54167, SN54LS157, SN54S157 . . . J OR W PACKAGE SN54L157 . . . J PACKAGE SN74157, SN74L157, SN74LS157, SN74S157 . . . J OR N PACKAGE

SN54LS158, SN54S158 . . . J OR W PACKAGE SN74LS158, SN74S158 . . . J OR N PACKAGE (TOP VIEW)

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)     |          |    |     |     |    | •   | •  | •   |    |    | •  |     | ٠  |    | ٠   |     | •   |    | • | • |   |   |  | •  | •   | •   |      | 7 V   |

|--------------------------------------|----------|----|-----|-----|----|-----|----|-----|----|----|----|-----|----|----|-----|-----|-----|----|---|---|---|---|--|----|-----|-----|------|-------|

| Input voltage: '157, 'L157, 'S158    |          |    |     |     |    |     | ٠  |     |    |    |    |     |    |    |     |     |     |    |   |   |   | , |  |    |     |     |      | 5.5 V |

| 'LS157, 'LS158 .                     |          |    |     |     |    |     |    |     |    |    |    |     |    |    |     | ٠   |     |    |   |   |   |   |  |    |     |     | •    | 7 V   |

| Operating free-air temperature range | <b>:</b> | SN | 154 | 1'. | SN | 154 | L  | , S | NE | 41 | S' | , S | N5 | 45 | ° C | irc | uit | ts |   |   | × | ٠ |  |    | 55° | C   | to   | 125°C |

|                                      |          | SN | 174 | ľ,  | SN | 174 | 1L | , S | N7 | 41 | S' | S   | N7 | 45 | ' C | irc | uit | ts |   |   |   |   |  |    | (   | )°C | : 10 | 70°C  |

| Storage temperature range            |          |    |     |     |    |     |    |     |    |    |    |     |    |    |     |     |     |    |   |   |   |   |  | -6 | 35° | 'C  | to   | 150°C |

NOTE 1: Voltage values are with respect to network ground terminal.

# TYPES SN54LS157, SN54LS158, SN54S157, SN54S158, SN74LS157, SN74LS158, SN74S157, SN74LS158 QUADRUPLE 2-LINE-TO-1-LINE DATA SELECTORS/MULTIPLEXERS

PET CPU BOARD

PET-SHACK SOFTWARE HOUSE